EECS 140 Lab

From ITTC

Contents

Announcements

- No labs during first week of classes.

- Labs start from 01/27/20

Lab Information

All labs for Fall 2019 start on Tuesday Jan 27th, 2020.

Location: 2010 Eaton Hall

* Monday : 08:00 - 09:50 AM - Pramil * Tuesday : 08:00 - 09:50 AM - Sharmila * Tuesday : 10:00 - 11:50 AM - Kishanram Kaje * Tuesday : 12:30 - 02:20 PM - Kishanram Kaje * Wednesday : 08:00 - 09:50 AM - Lazarus * Wednesday : 11:00 - 12:50 PM - Sharmila * Thursday : 08:00 - 09:50 AM - Pramil * Thursday : 10:00 - 11:50 AM - Amin * Thursday : 12:30 - 02:20 PM - Amin * Friday : 08:00 - 09:50 AM - Lazarus

Graduate Teaching Assistant(s)

- Kishanram Kaje, kaje@ku.edu

- Office - Eaton 2010/3029 (Email beforehand)

- Office Hours - Tu - 02:20 PM-04:20 PM

- Lazarus Francis S, sflazarus@ku.edu

- Office - Eaton 2010/2029 (Email beforehand)

- Office Hours - W 10:00 to 11:00 AM and F 10:00 to 11:00 AM

- Amin Shojaei, amin.shojaei@ku.edu

- Office - Eaton 2010/3029 (Email beforehand)

- Office Hours - F 09:00 to 11:00 AM

- Pramil Paudel, pramil.paudel@ku.edu

- Office - Eaton 2010/3029 (Email beforehand)

- Office Hours - M 10:00 to 11:00 AM and Th 10:00 to 11:00 AM

- Sharmila Raisa, sharmila@ku.edu

- Office - Eaton 2010/3006 (Email beforehand)

- Office Hours - Tu - 10:00 AM-12:00 PM

- Note: Please include [EECS 140] and your session in the subject line when you email your GTA.

Course Instructor(s)

- Dr. David Petr, dwp@ku.edu

- Office Hours - TR 11:30 to 12:30 PM and W 1:30 to 2:30PM

- Dr. David Johnson, davidojohnson@ku.edu

- Office Hours - M 01:00 to 3:00 PM and F 8:45-10:45 AM

Lab Report Format

- The lab report format is a simplified version of the lab report formats that you will use for the rest of your educational (and professional) engineering career.

- Use the template provided in the handout by your GTA when writing your lab reports. All sections are clearly defined for your convenience.

- The template is for reference for minimum requirements on a Lab report. You'll need to explain your work clearly along with your contributions in the lab plus whatever requirements mentioned by GTA.

Lab Schedule

VHDL in Vivado Labs

- This [Introduction to Vivado Tutorial] will teach you how to use Vivado.

- This VHDL tutorial will teach about the VHDL language, its fundamentals, and how to represent a simple circuit in VHDL.

- This Modular VHDL tutorial will teach about the using components in VHDL, and creating larger entities by structural design.

- This Digilent FPGA Board Basys 3™ FPGA Board will be used in the lab.

- Digital Design Using Digilent FPGA Boards: VHDL/ Active-HDL Edition by Richard E. Haskell and Darrin M. Hanna

Lab 1: Introduction FPGA Programming with Vivado

- Become familiar with Vivado and apply it to program a simple AND gate on your Basys-3 FPGA board

Lab 2: Introduction to VHDL

- Learn the basics about modern programmable logic and become familiar with Vivado and Adept software

Lab 3: Implementation of nuclear power plant control circuit

- Use VHDL to design the nuclear power plant control circuit and implement this design on Basys3 board

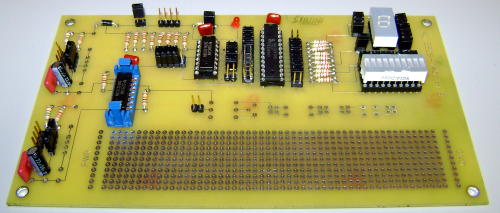

Printed Circuit Boards (PCB) Labs

Lab 4: Introduction to prototype board

- Solder power circuit, input switch circuit, output LED circuit and perform initial board test

Lab 5: Implementing a SOP Expression on Prototyping board

- Solder IC sockets, bypass capacitors, power and ground buses and interconnections headers.

VHDL + FPGA Labs

Lab 6: 7-Segment Display

- Create a seven segment display driver.

Lab 7: Introduction to Structural VHDL models

- Learn basics of structural VHDL models and design simple circuits using structural VHDL.

Lab 8: Four Bit Adder with Double 7-Segment Display

- Create a binary 4-bit adder and display the result on two 7-segment displays. Learn about VHDL code modularization.

Lab 9: Arithmetic Logic Unit

- Add multiple operations to our circuit. Allow the selection of operations, while still using the 7-segment outputs and a multiplier.

Lab 10: Scrolling Display

- Use modular VHDL to display a scrolling phrase on the FPGA.

Lab 11: Decoder and Encoder

- Implementation of Decoder and Encoder.

Lab 12: Latches, Flip-flops, and Registers

- Investigate latches, flip-flops, and registers.

Resources

This class will focus on using the Altera Flex 10K-UP2 Board along with the associated Altera Max+plus II software.

- EECS Shop

- Resistor Color Code

- Resistor Calculator

- Facebook Group: I Hate VHDL!!!!

- Capacitor Coding