Eecs388

EECS 388 - Computer Systems & Assembly Language

Dr. Andrews, and his wiki materials have moved to the University of Arkansas at UARK CSDL Wiki. Please follow this link to directly access the New UARK 388 page.

Contents

- 1 EECS 388 - Computer Systems & Assembly Language

- 1.1 Class Information

- 1.2 Course Description

- 1.3 Lecture Schedule

- 1.4 Homework

- 1.5 Resources

- 1.6 Documentation Repository

- 1.7 Tool Repository

- 1.8 Lab Repository

- 1.8.1 How to build a basic SoC

- 1.8.2 GPIOs + Basic MicroBlaze System

- 1.8.3 ChipScope + IBA + Microblaze System

- 1.8.4 Custom IP Cores + MicroBlaze System

- 1.8.5 Encryption Core + MicroBlaze System

- 1.8.6 MicroBlaze Assembly Programming

- 1.8.7 UART-based I/O + Assembly

- 1.8.8 Interrupt Driven MicroBlaze System

- 1.8.9 Dual-Core Microblaze System

- 1.8.10 Simple "Simon" Game

- 1.9 Copyright

Class Information

Class: EECS 388

- Days : Monday and Wednesday (MW)

- Time : 12:30 PM - 1:45 PM

Instructor(s)

- Dr. David Andrews, dandrews@ittc.ku.edu

- Office - Eaton 2032 - MW 2:00 - 3:00

Teaching Assistant(s)

- Jason Agron, jagron@ittc.ku.edu

- Office - Nichols 145 - (MW 1:00 - 3:00, and by appt.)

- Office - Eaton 3043 - (R, 4:45 - 5:00 IN LAB, and by appt.)

- Fabrice Baijot, bricefab@ittc.ku.edu

- Office - Eaton 3043 - (TBD)

Course Description

"Internal organization of microprocessor and microcontroller systems; programming in assembly language; input and output system; controlling external devices. The course will focus on one or two specific microprocessors and computer systems."

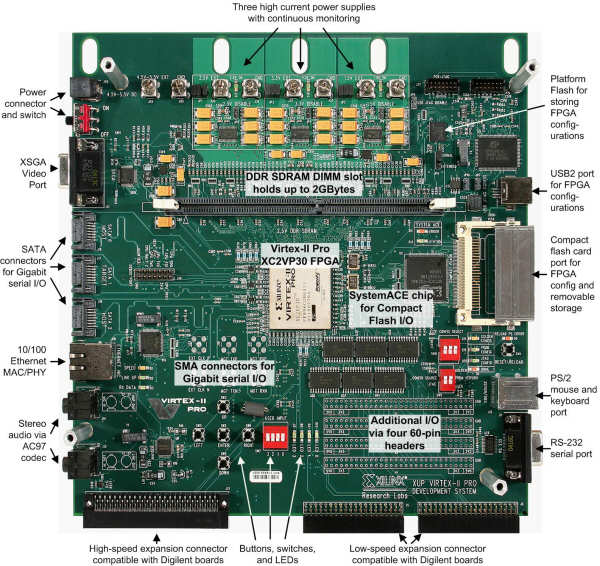

This class will make use of the Xilinx/Digilent XUP-V2P (XUP-V2Pro) Development Board. This development board contains a modern Virtex-II Pro Platform FPGA along with various peripherals such as Ethernet, USB, Audio In/Out, LEDs, buttons, switches, VGA, etc. Various System-On-Chip (SoC) architectures will be developed during this class, all of which will be implemented within the fabric of the FPGA. Most, if not all, of the SoCs developed during this class will use the MicroBlaze processor; a soft 32-bit processor core developed by Xilinx. The instruction set architecture, or ISA, of the MicroBlaze will be studied and used throughout this class, in order to teach students the relationships between high-level languages, assembly language, and the actual hardware implementation of computer systems.

Lecture Schedule

- Week 1 Course Introduction and Review

- Monday 8/20: File:Introduction.pdf - Course Requirements and Embedded Systems Overview

- Wednesday 8/22: Reviews

- File:Review.pdf - Address Ranges, Memory Maps, Data Types

- File:Pointers.pdf - Review of Pointers

- Week 2 Introduction to Tools

- Monday 8/27: File:Edk baseSystemBuilder.pdf - Step-by-step instructions on how to build a system using EDK/XPS.

- Introduction to Xilinx toolset.

- Basic system design within EDK.

- Introduction to SW development.

- Wednesday8/29: You will show how to create and run the hello world program in lab

- Monday 8/27: File:Edk baseSystemBuilder.pdf - Step-by-step instructions on how to build a system using EDK/XPS.

- Week 3 Introduction to ISA's

- Monday 9/3: Labor Day Holiday

- Wednesday 9/5: File:Gpbio.pdf - An introduction to the General Purpose I/O Core Used in Lab

- File:Opb gpio.pdf - Xilinx OPB General Purpose I/O Core Document

- Week 4 Introduction to the Microblaze CPU

- Both lectures this week will work from the MicroBlaze Processor Reference Guide

- Monday 9/10: MicroBlaze Processor Reference Guide (ISA Documentation, etc.)

- RTL description of Microblaze; GP Registers, MSR, PC, ALU, Shifter. Instruction encodings TypeA and TypeB

- Wednesday 9/12: Arithmetic Instructions. Encoding instructions into TypeA and TypeB. Imm instruction

- Week 5 Microblaze ISA continued

- Monday 9/17: data layout in Memory, data movement instructions, word,half-word,byte alignment

- Wednesday 9/19: Generaal bus signals for data transfer, AS, READY, Data, Address

- Week 6 Conditional Instructions

- Monday 9/24: Flowcharts pseudo code, conditional and unconditional branch instructions

- Wednesday 9/26: assembler coding examples

- Week 7: Protocol Stacks

- Monday 10/1: General Stack operation, branching and linking

- Wednesday 10/3: Stack Frames and Data Passing

- Week 8 Stack Operations continued

- Monday 10/8: ABI Standards Interface Registers

- Wednesday 10/10: Nested Calls and Recursion on the Stack

- Week 9 Stack examples, Introduction to Co-Processor Interfacing

- Monday 10/15: More stack operation examples; 388 standards

- Wednesday 10/17: Address Maps and Interface Registers

- Week 10 Serial and Parallel Interface Devices

- File:8251A.pdf - Intel UART Data Sheet

- OPB-UARTLITE - IP Core Documentation

- Monday 10/22: Serial bit stream configuration. Start/Stop/Parity/Data Transmission Protocols

- Wednesday 10/24: UART Mode/Command/Status Registers

- Week 11 UART Continued

- Monday 10/29: UART and UART Lite Setup and Polling Software Routines

- Wednesday 10/31: Overview of Material Covered So Far

- Week 12 Review and Exam

- Monday 11/ 5: Questions for Exam 1

- Wednesday 11/7: Exam 1

- Week 13 Exam Solutions and Introduction to Interrupts

- Monday 11/12: Exam 1 solutions

- Wednesday 11/14: Introduction to Interrupt Operations

- File:Opb intc.pdf - Xilinx Interrupt Lite Core

- Week 14

- Monday 11/19: OPB_INTC Registers

- Wednesday 11/21: Thanksgiving Break

- Week 15 Interrupts and Timers

- File:Opb timer.pdf - Xilinx Timer Core

- Monday 11/26: Interrupt Handler Routines and Examples

- Wednesday 11/28: Introduction to Timers

- Week 16 Timers Continued

- Monday 12/3: OPB_Timer Setup

- Wednesday 12/5: Timer Usage

Homework

Assignments

- File:Homework1.pdf - HW #1, due September 19, 2007

- File:Homework2.pdf - HW #2, due September 26, 2007

- File:Homework3.pdf - HW #3, due October 17, 2007

- File:Homework4.pdf - HW #4 due October 31, 2007

- File:Homework5.pdf - Updated: HW #5 due December 5, 2007

Resources

This class will focus on using Xilinx Platform FPGAs along with the associated Xilinx EDK toolset (XPS + ISE). Much of the class materials can be found online on either this website and/or the Xilinx homepage. All of the class projects will make use of the XUP-V2P (XUP-V2Pro) development board which contains a Xilinx Virtex-II Pro 30 FPGA.

Documentation Repository

Lab Instructions

- File:ReportFormat.pdf - EECS 388 Lab Report Format & Instructions

- File:Lab demos.pdf - EECS 388 Lab Demo Instructions

Basic Information

- Xilinx XUP-V2P Home Page (Good starting point for XUP documentation)

- XUP-V2P User Constraints Files (UCFs)

- MicroBlaze Processor Reference Guide (ISA Documentation, etc.)

- MicroBlaze Software Reference Guide (How to build SW for MB, etc.)

- Xilinx XST User's Guide (Good HDL coding templates and tips)

EDK/XPS Information

- Description of EDK/XPS Project Files

- EDK Reference Manual

- EDK MicroBlaze Tutorial (NOTE - for a Spartan FPGA)

- EDK PowerPC Tutorial (NOTE - for a Virtex-4 FPGA)

- Virtual Platforms - Simulating a MicroBlaze based system and it's peripherals

Examples (XAPPs)

- xapp967 - Creating an OPB IPIF-based IP and Using it in EDK

- xapp778 - Using and Creating Interrupt-Based Systems

- xapp529 - Connecting Customized IP to the MicroBlaze Processor Using Fast Simplex Link (FSL) Channels

- xapp730 - Getting Started with uClinux on the MicroBlaze Processor

ChipScope Pro Information

- HOWTO - Instantiating ChipScope Pro Cores within EDK

- HOWTO - Debugging HW with ChipScope Pro

- HOWTO - Monitoring HW Signals with ChipScope Pro

Tool Repository

- File:Xup xbd.zip - 10.1 compatible Xilinx Board Definition (XBD) file for the XUP-V2P (Thanks Wes).

Lab Repository

All lab projects can be found through the following link: EECS 388 Lab Page.

How to build a basic SoC

- Lab 1: File:Edk baseSystemBuilder.pdf - Step-by-step instructions on how to build a system using EDK/XPS.

- Project Purpose:

- Introduction to Xilinx toolset.

- Basic system design within EDK.

- Introduction to SW development.

GPIOs + Basic MicroBlaze System

- Lab 2: File:Edk memMapIO.pdf - Step-by-step instructions on how to interact with GPIOs from SW

- File:Pointers.pdf - Basic review of pointer constructs in C

- File:GPIOpointers.c - Example C code of how to interact with GPIOs using pointers

- Project Purpose:

- Basic system design within EDK

- Simple SW development for MicroBlaze

- Simple lesson in memory-mapped I/O via GPIOs

ChipScope + IBA + Microblaze System

- Lab 3: File:Edk chipscope.pdf - Step-by-step instructions on how to use ChipScope and the Integrated Bus Analyzer.

- File:AddBRAM.doc - Step-by-step instructions on how to add memory to the OPB bus.

- OPB Bus Structure - OPB v2.0 Documentation

- Project Purpose:

- Introduction to ChipScope Pro toolset

- How to monitor and debug hardware in real-time

Custom IP Cores + MicroBlaze System

- Lab 4: File:Edk customCores.pdf - Step-by-step instructions on how to create/use custom IP cores using EDK/XPS.

- File:CustomIP.pdf - Detailed step-by-step instructions on how to create/add/use Custom IP cores within EDK.

- File:ProjectPermissions.doc - Instructions on how to setup project permissions for XPS.

- Project Purpose:

- Demonstrate how to create custom OPB-based IP cores

- How to communicate with memory-mapped devices

Encryption Core + MicroBlaze System

- File:NewEncryptTest.zip - Use this system!! (the encryption core is already in the project, all that is needed is SW)

- Lab 5: File:CustomIP encryption.pdf - Create a system that interacts with a custom encryption IP core.

- File:User logic.vhd - Modified user logic file that implements Caesar Cipher Encryption.

- Project Purpose:

- How to interact with a simple HW-based accelerator

- How to write SW drivers for memory-mapped devices.

MicroBlaze Assembly Programming

- Lab 6: File:Assembly.pdf - A small introduction to programming control structures in the MicroBlaze ISA

- MicroBlaze ISA - MicroBlaze ISA Documentation

- File:AssemblyTest.s - Simple MicroBlaze assembly program

- Uses the pre-defined "print" and "xil_printf"

- Uses a control loop with a decrementing variable

- Project Purpose:

- Learn the MicroBlaze ISA

- How to write control structures in assembly languages:

- Conditionals (IF-THEN-ELSE)

- Loops (FOR, WHILE)

- Function call semantics

UART-based I/O + Assembly

- Lab 7: File:UART Lab Instr.doc - UART-based I/O Lab Instructions

- OPB-UARTLITE - IP Core Documentation

- File:HintsUART.txt - Hints on how the UART works and how to interact with it.

- Project Purpose:

- Learn how to communicate with a UART

- Learn the MicroBlaze ISA

- Learn how to write a simple output driver

Interrupt Driven MicroBlaze System

- Lab 8: File:Edk interrupts.doc - (DOC) Step-by-step instructions on how to create interrupt-based systems.

- File:Edk interrupts.pdf - (PPT) Step-by-step instructions on how to create interrupt-based systems.

- Project Purpose:

- Demonstrate how to connect HW devices up to CPU's interrupt ports

- How to write interrupt handlers

- How to configure MicroBlaze interrupts

- How to setup/configure an interrupt controller

- How to setup/configure bus-based timers

Dual-Core Microblaze System

- Lab 9: File:DualMicroblaze.zip Dual-core MicroBlaze system for the XUP development board

- File:DualCoreMicroblaze.pdf Block diagram of the dual-core MicroBlaze system

- Project Purpose:

- Introduction to MPSoC

- How to build/program an FPGA-based multiprocessor system (with MicroBlaze CPUs)

- Introduction to FSLs (MB's co-processor interface)

- Introduction to message-passing

- Introduction to MPSoC

Simple "Simon" Game

- Lab 10: ??? - Create a custom application on the XUP

- File:Simon.tar.gz MicroBlaze SoC implementing the "simon" game

- Project Purpose:

- How to interact with memory-mapped peripherals:

- LEDs, Buttons, and AC-97 Codec (Beep Function)

- Application development for MicroBlaze

- How to interact with memory-mapped peripherals:

Copyright

All lab materials created by Jason Agron (Summer, 2007). Feel free to use the labs for educational purposes, but please give credit to Jason and the CSDL lab at the University of Kansas.