# The Xilinx EDK Toolset: Custom IP Cores

Creating and using custom IP cores By Jason Agron

### What is an IP Core?

- IP = Intellectual Property

- Why is it called this?

- In our case, IP is "soft".

- ➢ Not physical.

- It is merely a (soft) "description" of a device.

- ➢ Usually in VHDL or Verilog.

- Why is this cool?

- Can be open-source.

- Can be understood and studied.

- Can be customized.

- Portable...

- It is a model can be simulated or implemented.

- FPGA.

- ASIC.

### Where Do IP Cores Come From?

- For those who do not design HW...

- Many are provided by vendors.

- Xilinx provides many within it's IP catalog.

- For those that can design HW...

- You can make your own.

- From scratch.

- Using other soft/hard components.

# What Is A Typical IP Core?

- Any digital device that you have seen could be implemented as a soft IP core...

- As long as it can fit "inside" an FPGA.

- Some examples:

- CPUs

- Graphics cards

- Network cards

- Specialized processors (DSPs, FPUs, DataFlow)

- Memory banks

### What Do Soft IP Cores Enable?

- They enable a programmer/designer to combine pieces of IP at will in order to form a custom SoC within an FPGA.

- No soldering!

- Just connect the inputs and outputs of the respective IP cores.

- Done within VHDL/Verilog or a scripting language.

### How To Create Custom IP Cores

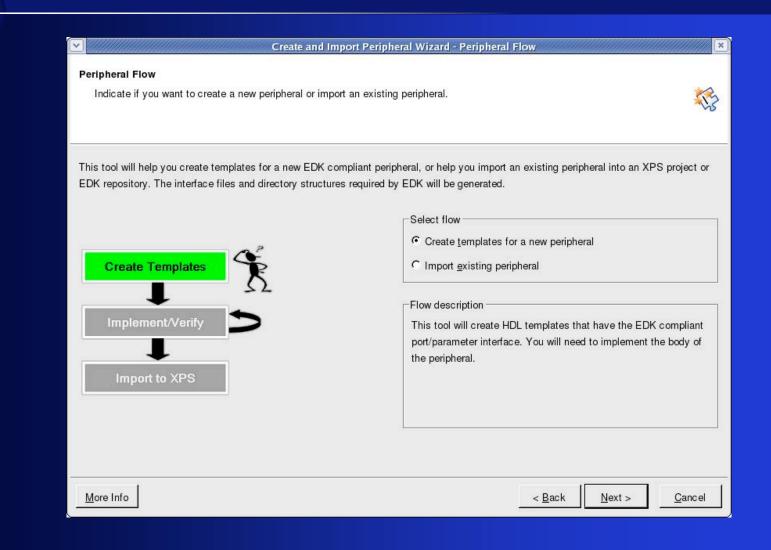

- XPS has a built-in wizard...

- Click on "Hardware..."

- Select "Create or Import Peripheral..."

- The wizard allows one to...

- Create a new piece of IP.

- Select it's interface (PLB, OPB, FSL).

- Select default features to include.

- Select it's generation parameters...

- VHDL or Verilog, etc.

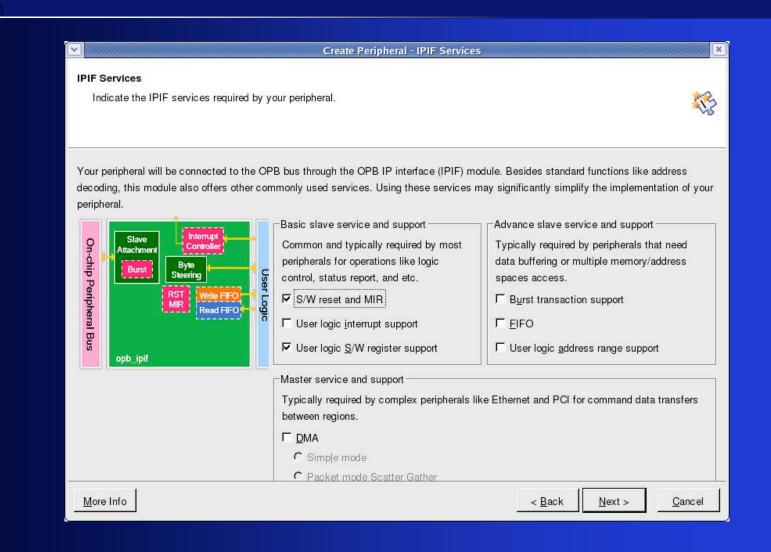

### Our Goal

- Create a custom IP core...

- With an OPB interface.

- With 4 SW-accessible registers

- With Reset/MIR support.

- Implemented in VHDL.

- The result:

- Very simple IP core.

- 4 storage locations (readable/writable).

# **XPS - Creating Custom IP**

|                                                           |                                                            |                 |                    |                    |            | Wed May 30, 1:51 PM 🔇 |

|-----------------------------------------------------------|------------------------------------------------------------|-----------------|--------------------|--------------------|------------|-----------------------|

| Xilinx Platfor                                            | m Studio - /users/jagron/388l                              | abs/chipscopeME | 3/system.xmp - [Sy | stem Assembly View | <b>i</b> ] |                       |

| Eile Edit View Project Hardware Software Device Configura | ation <u>D</u> ebug Si <u>m</u> ulation <u>W</u> ind       | ow <u>H</u> elp |                    |                    |            | _15                   |

| 🗋 🎓 🖥 🦕 🛛 📴 🕅 🗑 🛤 Generate <u>N</u> etlist                | 🖸 🛛 🖉 🗛 🔝 🏀 🖉 🛛                                            | 🗠 📥 🗋 🏚 🗍 🖩     | iff 🎥 🛛 🐹 💥 🗍 🕻    | a 🛛 🔤 🖉            | 8 0 🔁 🕅    |                       |

| B Generate Bitstream                                      | Filters                                                    |                 | 12                 |                    |            |                       |

| Project Applications IF                                   | 👻 🤄 Bus Interface 🤇 Ports 🤇 Addresses 👔 Connection Filters |                 |                    |                    |            |                       |

| Platform                                                  | Name                                                       | Bus Connection  | IP Type            | IP Version         |            |                       |

| Project Files                                             | terroblaze 0                                               | Bus connection  | microblaze         | 5.00.c             |            |                       |

| MHS File: system.mh Debug Configuration                   | ture opb                                                   |                 | opb v20            | 1.10.c             |            |                       |

| MSS File: system.ms Check and View Core Licenses          |                                                            |                 | lmb v10            | 1.00.a             |            |                       |

| UCF File: data/systen 👺 Clean Netlist                     | t] ⊕-≪dlmb                                                 |                 | Imb_v10            | 1.00.a             |            |                       |

| - IMPACT Command Fi                                       |                                                            |                 | opb_mdm            | 2.00.a             |            |                       |

| Implementation Option                                     |                                                            |                 | Imb_bram_if_cntlr  | 2.00.a             |            |                       |

| Bitgen Options File: e 🗳 Clean Hardware                   |                                                            |                 | Imb_bram_if_cntlr  | 2.00.a             |            |                       |

| Project Options                                           | ⊞- <b></b> →RS232_Uart_1                                   |                 | opb_uartlite       | 1.00.b             |            |                       |

|                                                           | E->LEDs_4Bit                                               |                 | opb_gpio           | 3.01.b             |            |                       |

| -Netlist: TopLevel                                        | DIPSWs_4Bit                                                |                 | opb_gpio           | 3.01.b             |            |                       |

| Implementation: XPS                                       | E- PushButtons_5Bit                                        |                 | opb_gpio           | 3.01.b             |            |                       |

|                                                           | Chipscope_icon_0                                           |                 | chipscope_icon     | 1.00.a             |            |                       |

| Reference Files                                           |                                                            | 0               | chipscope_opb_ib   |                    |            |                       |

| iter Log Files                                            | □ • • Imb_bram                                             |                 | bram_block         | 1.00.a             |            |                       |

| Synthesis Report Files                                    | ⊞ <b>&gt;</b> dcm_0                                        |                 | dcm_module         | 1.00.a             |            |                       |

| System A                                                  | Assembly View1                                             |                 |                    |                    |            |                       |

|                                                           |                                                            |                 |                    |                    |            |                       |

|                                                           |                                                            |                 |                    |                    |            |                       |

|                                                           |                                                            |                 |                    |                    |            |                       |

|                                                           |                                                            |                 |                    |                    |            |                       |

|                                                           |                                                            |                 |                    |                    |            |                       |

|                                                           |                                                            |                 |                    |                    |            |                       |

|                                                           |                                                            |                 |                    |                    |            |                       |

|                                                           |                                                            |                 |                    |                    |            |                       |

|                                                           |                                                            |                 |                    |                    |            |                       |

|                                                           |                                                            |                 |                    |                    |            |                       |

|                                                           |                                                            |                 |                    |                    |            |                       |

| 4                                                         |                                                            |                 |                    |                    |            |                       |

| - J<br>Output Warnings Errors                             |                                                            |                 |                    |                    |            |                       |

### **XPS - Wizard Startup**

## **XPS - Create New Peripheral**

### **XPS - Select Storage Location**

|                                                   | Create Peripheral - Repository or Proj                                      | iect                                     |

|---------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------|

| epository or                                      | Project                                                                     |                                          |

| Indicate wh                                       | ere you want to store the new peripheral.                                   | ***                                      |

|                                                   |                                                                             |                                          |

|                                                   |                                                                             |                                          |

|                                                   | al can be stored in an EDK repository, or in an XPS project. When stored in | an EDK repository, the peripheral can be |

| ccessed by m                                      | ultiple XPS projects.                                                       |                                          |

|                                                   |                                                                             |                                          |

| C To an EDP                                       | Cuser repository (Any directory outside of your EDK installation path)      |                                          |

| <u>R</u> epositor                                 | w.                                                                          | * Browse                                 |

| Hopoonton                                         |                                                                             | BIO <u>W</u> BOIL                        |

| Hopoundi                                          | 7· ]                                                                        |                                          |

| To an <u>X</u> PS                                 |                                                                             |                                          |

|                                                   |                                                                             | <u>Brows</u> e                           |

| To an <u>X</u> PS                                 | S project                                                                   |                                          |

| To an <u>X</u> PS                                 | S project                                                                   |                                          |

| To an <u>X</u> PS                                 | S project                                                                   |                                          |

| To an <u>X</u> PS                                 | S project                                                                   |                                          |

| ি To an <u>X</u> P\$<br>Project:                  | S project                                                                   |                                          |

| ি To an <u>X</u> PS<br>Project:<br>Peripheral wil | S project<br>/users/jagron/388labs/chipscopeMB/                             |                                          |

| ি To an <u>X</u> PS<br>Project:<br>Peripheral wil | S project<br>//users/jagron/388labs/chipscopeMB/                            |                                          |

# **XPS - Select Name & Version**

| Name and Version                                                                                                |                                                                  |                                        |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------|

| Indicate the name and version o                                                                                 | your peripheral.                                                 |                                        |

| Enter the name of your peripheral. 1                                                                            | nis name will be used as the top HDL design entity.              |                                        |

| Name: opb_customcore                                                                                            |                                                                  |                                        |

| Version: 1.00.a                                                                                                 |                                                                  |                                        |

| Major <u>r</u> evision: Minor revision<br>1 1 1<br>00 1                                                         | <u>H</u> ardware/Software compatibility revision:<br>a           |                                        |

|                                                                                                                 |                                                                  |                                        |

| ⊢Logical library name: opb_custom                                                                               | ore v1 00 a                                                      |                                        |

| La Constante de la Constante de Constante de la | or generated by this tool) used to implement this peripheral m   | ust be compiled into the logical libra |

| named above. Any other logical li                                                                               | raries referred to in your HDL are assumed to be available in th |                                        |

| liego or in Lik repositorios india                                                                              | ted in the XPS project settings.                                 |                                        |

# **XPS** - Interface Selection

| Create Peripheral - Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Bus Interface<br>Indicate the bus interface supported by your peripheral.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

| To which bus will this peripheral be attached?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

| Con-chip Peripheral Bus (OPB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

| C Processor Local Bus (PLB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

| ATTENTION         Refer to the following documents to get a better understanding of how user peripherals connect the IPIF interconnection standards.         CoreConnect Specification         OPB IPIF Specification for slave only peripherals         OPB IPIF Specification for master/slave peripherals         PLB IPIF Specification for slave only peripherals         PLB IPIF Specification for master/slave peripherals         PLB IPIF Specification for master/slave peripherals         PLB IPIF Specification for master/slave peripherals         NOTE: Other bus interfaces are not supported by the wizard in this release. | t to the CoreConnect(TM) buses through |

| More Info                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | < Back Next > Cancel                   |

### **XPS - Feature/Service Selection**

# **XPS - S/W Register Selection**

| User S/W Register         Configure the software accessible registers in your peripheral.         The software accessible registers will be implemented in the user-logic module of your peripheral. These registers byte, half-word or word boundaries. The following fields determine the characteristics of the registers.         Number of software accessible registers:         Qata width of each register: | are addressable on the   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| byte, half-word or word boundaries. The following fields determine the characteristics of the registers.          Number of software accessible registers:         Data width of each register:         32                                                                                                                                                                                                          | are addressable on the   |

|                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |

| Write Mode<br>Instead of the usual <i>acknowledge write</i> behavior, an alternative kind of write behavior, <i>posted write</i> , is also suppowrite behavior, the IPIF unconditionally acknowledges the write transactions to the OPB on the earliest clock cycl and improves performance. When posted writes are enabled, it is assumed that the custom user logic will retire to local storage.                 | le, thus reduces latency |

| <ul> <li>C Enable posted write behavior</li> <li>C Disable posted write behavior for normal acknowledged write behavior</li> <li>C Allow dynamic posted/acknowledged write behavior controlled by user logic (IP2Bus PostedWrInh)</li> </ul>                                                                                                                                                                        |                          |

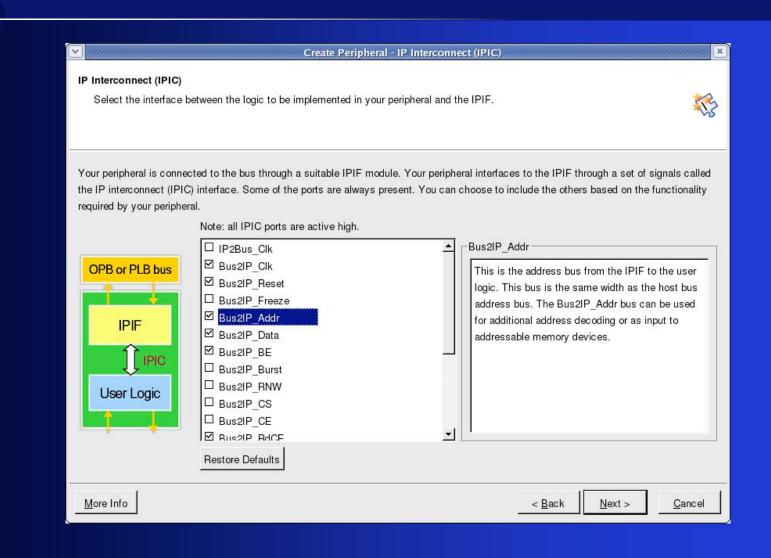

### **XPS - IPIC Configuration**

# **XPS - Simulation Support**

| (OPTIONAL) Peripheral Simulation<br>Generate optional files for simulat                        | Create Peripheral - (OPTIONAL) Peripheral Simulation Support<br>Support<br>tion using Bus Functional Models (BFM).                                                                                                                                                                                                                                                          |               |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| The EDK provides a BFM simulation<br>HDL and Bus Functional Language (B<br>OPB Device (master) | platform to help you simulate your peripheral. Indicate if you want this tool to g<br>BFL) stimulus file for the target bus.<br>Generate BFM simulation platform for ModelSim-SE or ModelSim-I<br>This feature requires that you have accepted the associated IBM I<br>installed the BFM toolkit. The link below shows how:<br><u>BFM Toolkit Installation Instructions</u> | 2             |

| BFM Synch Bus                                                                                  |                                                                                                                                                                                                                                                                                                                                                                             |               |

| More Info                                                                                      | < <u>B</u> ack                                                                                                                                                                                                                                                                                                                                                              | Next > Cancel |

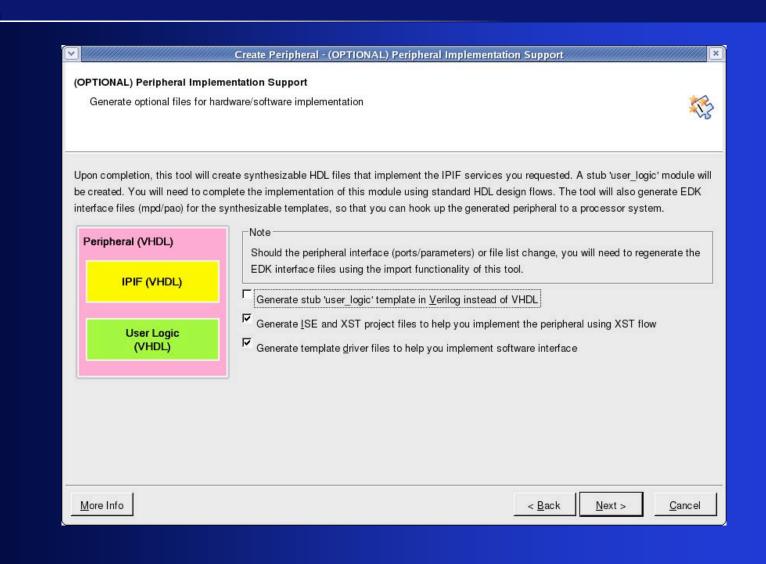

# **XPS - Implementation Support**

# **XPS - IP Creation Complete**

#### **Create Peripheral - Finish**

#### **Congratulations!**

When you click Finish, HDL files representing your peripheral will be generated. You will have to implement the functionality of your peripheral in the stub 'user\_logic' template file.

**IMPORTANT**: If you make any interface changes to the generated peripheral (including peripheral name, version, ports and parameters), or any file changes (add or remove files), you will need to regenerate the EDK interface files by using this tool in the Import mode.

Thank you for using Create and Import Peripheral Wizard! Please find your ▲ peripheral hardware templates under /users/jagron/388labs/chipscopeMB/pcores/opb\_customcore\_v1\_00\_a and

peripheral software templates under /users/jagron/3881abs/chipscopeMB/drivers/opb\_customcore\_v1\_00\_a

respectively.

Peripheral Summary:

top name : opb\_customcore version : 1.00.a type : OPB slave features : slave attachement mir/rst register

< <u>B</u>ack <u>F</u>inish

Cancel

### IP Created, Now What?

- We have just created a piece of IP that is now in the project repository.

- How do we use it?

- It must first be added into the system.

- Added into the system.

- Connected to the bus.

- Configured (address range, ports).

- How do we see it?

- (HINT) IP Catalog Tab

# **XPS - Adding IP To The System**

| Eile Edit View Project Hardware Software Device Con | tform Studio - /users/jagron/388labs/c                         |                                                         |                         |            |  |

|-----------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------|-------------------------|------------|--|

|                                                     |                                                                |                                                         | [System Assembly View1] |            |  |

|                                                     | -                                                              |                                                         |                         |            |  |

| III M @ @ X ∾ ∾  🖕 🛪 📬   4 🖌 🖬 🔄 🗌                  | D-P 😼 🖸 😠 🗍 B-B 🔠 🏀 🗍 🜌 🚥 💈                                    | 🏾 🗋 🔛 🛗 🔛 🏠 🖉                                           |                         | <b>k</b> ? |  |

|                                                     | Filters                                                        |                                                         |                         |            |  |

| Project Applications IP Catalog                     | LL 😁 🕫 Bus Interface 🤆 Ports 🤇                                 | Bus Interface C Ports C Addresses    Connection Filters |                         |            |  |

| В                                                   |                                                                | s Connection IP Type                                    | IP Version              |            |  |

|                                                     | te- → microblaze 0                                             | microblaze                                              | 5.00.c                  |            |  |

| Name Version                                        | tti → microbiaze_0                                             | opb v20                                                 | 1.10.c                  |            |  |

| Communication High-Speed                            |                                                                | Imb v10                                                 | 1.00.a                  |            |  |

| + Communication Low-Speed                           | ture dimb                                                      | Imb_v10                                                 | 1.00.a                  |            |  |

| DMA                                                 | debug module                                                   | opb mdm                                                 | 2.00.a                  |            |  |

| * Debug                                             | tu o debug_ntcodie<br>tu o debug_ntcodie<br>tu o debug_ntcodie | Imb bram if c                                           |                         |            |  |

| + FPGA Reconfiguration                              | O ● Units_citin<br>U= ● ilmb_citin                             | Imb bram if c                                           |                         |            |  |

| T-General Purpose IO                                | ⊕- <b>⊘</b> RS232 Uart 1                                       | opb uartlite                                            | 1.00.b                  |            |  |

| Interrupt Control                                   | E->LEDs 4Bit                                                   | opb_gpio                                                | 3.01.b                  |            |  |

| - Memory Block                                      | ⊕- →DIPSWs 4Bit                                                | opb_gpio                                                | 3.01.b                  |            |  |

| * Memory Controller                                 | ⊕ • PushButtons 5Bit                                           | opb_gpio                                                | 3.01.b                  |            |  |

| PCI                                                 | ⊕ • • • • • • • • • • • • • • • • • • •                        | chipscope_icor                                          |                         |            |  |

| Peripheral Controller                               | thipscope_opb_iba_0                                            | chipscope_opb                                           |                         |            |  |

| Processor                                           |                                                                | bram block                                              | 1.00.a                  |            |  |

| Project Repository                                  |                                                                | dcm_module                                              | 1.00.a                  |            |  |

| opb customcore 1.00.a                               | a dom_o                                                        | dem_module                                              | 1.00.a                  |            |  |

| Reset Control Add IP                                |                                                                |                                                         |                         |            |  |

| Timer View MPD                                      |                                                                |                                                         |                         |            |  |

| Utility                                             | 1                                                              |                                                         |                         |            |  |

| T Verification                                      |                                                                |                                                         |                         |            |  |

|                                                     | tem Assembly View1                                             |                                                         |                         |            |  |

|                                                     | Contrastentialy viewi                                          |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         |            |  |

| 4                                                   |                                                                |                                                         |                         |            |  |

| Output Warnings Errors                              |                                                                |                                                         |                         |            |  |

| Calpar Hainings Linus                               |                                                                |                                                         |                         |            |  |

|                                                     |                                                                |                                                         |                         | 0          |  |

# **XPS - Connecting IP To Bus**

| 🛎 Applications Actions 🔍 🗏 🍞 🗾 🔮                                               |                                        |                              |                |                   |                       | 🕕 Wed May 30, 2:01 PM 🔇 |

|--------------------------------------------------------------------------------|----------------------------------------|------------------------------|----------------|-------------------|-----------------------|-------------------------|

|                                                                                |                                        | Studio - /users/jagron/388la |                | /system.xmp - [S  | ystem Assembly View1] |                         |

| <u>File Edit View Project Hardware Software Devic</u>                          |                                        |                              |                |                   |                       | <u>_16</u>              |

| A 🗈 🗗 🗶 🗠 📬 👘 📬 🛛 🖉 🖉 🖸                                                        | 8 00 😼                                 | , 🔽 🖹 🖹 🗞 📓 🎇 🛛 🖾            | 100 📥 🛐 🏫 🗍 🖩  | # 28 ] 🛛 💥 ] [    | 🖻 🕅 🛛 X 🛛 着 🗛 🗖 🗖     | N?                      |

| ×                                                                              |                                        | Filters                      |                | 19.<br>19.        |                       |                         |

| Project Applications IP Catalog                                                | OLL OBUS Interface C Ports C Addresses |                              |                |                   | ters                  |                         |

| •                                                                              | P M M<br>B B B                         |                              |                |                   |                       |                         |

| 0                                                                              |                                        | Name                         | Bus Connection | IP Type           | IP Version            |                         |

| Name 🗸 Version 🔺                                                               |                                        | microblaze_0                 |                | microblaze        | 5.00.c                |                         |

| Clock Control                                                                  |                                        |                              |                | opb_v20           | 1.10.c                |                         |

| Communication High-Speed                                                       |                                        | i⊞- <b>⊘</b> ilmb            |                | lmb_v10           | 1.00.a                |                         |

| Communication Low-Speed                                                        |                                        | t <mark>e</mark> -≪dlmb      |                | lmb_v10           | 1.00.a                |                         |

| T-DMA                                                                          |                                        | ⊞- <b>⊘</b> debug_module     |                | opb_mdm           | 2.00.a                |                         |

| ⊕-Debug                                                                        |                                        | ⊞ ≪dlmb_cntlr                |                | Imb_bram_if_cntlr | 2.00.a                |                         |

| E-FPGA Reconfiguration                                                         |                                        |                              |                | Imb_bram_if_cntlr | 2.00.a                |                         |

| General Purpose IO                                                             |                                        | B- RS232_Uart_1              |                | opb_uartlite      | 1.00.b                |                         |

| Interrupt Control                                                              | 1                                      | ⊕- <b>◇LEDs_4Bit</b>         |                | opb_gpio          | 3.01.b                |                         |

| Hemory Block                                                                   | I                                      | DIPSWs_4Bit                  |                | opb_gpio          | 3.01.b                |                         |

| Hemory Controller                                                              |                                        | D- PushButtons 5Bit          |                | opb gpio          | 3.01.b                |                         |

| ÷-PCI                                                                          |                                        |                              |                | chipscope icon    | 1.00.a                |                         |

| - Peripheral Controller                                                        |                                        |                              | 0              | chipscope opb ib  | a 1.00.a              |                         |

| ⊕ Processor                                                                    |                                        | e eopb customcore 0          |                | opb customcore    |                       |                         |

| Project Repository                                                             |                                        | SOPB                         | mb_opb         |                   |                       |                         |

| opb customcore 1.00.a                                                          | •                                      |                              |                | bram block        | 1.00.a                |                         |

| +-Reset Control                                                                |                                        | dcm 0                        |                | dcm module        | 1.00.a                |                         |

| ±-Timer                                                                        |                                        | - dom_o                      |                |                   |                       |                         |

| ⊕-Utility                                                                      |                                        |                              |                |                   |                       |                         |

| Verification                                                                   |                                        |                              |                |                   |                       |                         |

|                                                                                | Svetom A                               | ssembly View1                |                |                   |                       |                         |

| Assigned Driver opb_customcore 1.00.a<br>opb_customcore_0 has been added to th |                                        |                              |                |                   |                       |                         |

|                                                                                |                                        |                              |                |                   |                       | <u>د</u>                |

| Output Warnings Errors                                                         |                                        |                              |                |                   |                       |                         |

|                                                                                |                                        |                              |                |                   |                       |                         |

|                                                                                |                                        |                              |                |                   |                       |                         |

# **XPS - Locking Address Ranges**

|                                      | Xilinx Platform | Studio - /users/iagro | n/388labs/chip  | scopeMI  | B/svste     | em.xmp - [System Assem | blv View1i          | -   |

|--------------------------------------|-----------------|-----------------------|-----------------|----------|-------------|------------------------|---------------------|-----|

| Eile Edit View Project Hardware Soft |                 |                       |                 |          | an par para |                        | an) anama;          | _   |

| X 9 00 15 16 16 1 4 1 4 1            |                 |                       |                 |          | EE 00 20    |                        | x 6 8 0 5 19        |     |

|                                      |                 |                       |                 |          | 2021 690    |                        |                     |     |

| Project Applications IP Catalog      | T inters        |                       |                 |          |             | 1                      |                     |     |

|                                      | e Bus Inte      | rface C Ports C Add   | dresses Ge      | nerate A | ddress      |                        |                     |     |

| Ð                                    | Name Ad         | dress Base Address    | High Address    | Size     | Lock        | Bus Connection IP Type | IP Version Instance |     |

| Name Version                         | <b>_</b>        |                       | · · · · · · · · | U        |             |                        | mb_opb              |     |

| CIOCK CONTROL                        | SLMB            | 0x00000000            | 0x00003fff      | 16K      |             | dimb                   | dlmb_cntlr          |     |

| E-Communication High-Speed           | SLMB            | 0x00000000            | 0x00003fff      | 16K      |             | ilmb                   | ilmb_cntlr          |     |

| Communication Low-Speed              | SOPB            |                       |                 | U        |             | mb_opb                 | opb_customcore      | _0  |

| - DMA                                | SOPB            | 0x40000000            | 0x4000ffff      | 64K      |             | mb_opb                 | LEDs_4Bit           |     |

| B-Debug                              | SOPB            | 0x40020000            | 0x4002ffff      | 64K      |             | mb_opb                 | DIPSWs_4Bit         |     |

| FPGA Reconfiguration                 | SOPB            | 0x40040000            | 0x4004ffff      | 64K      |             | mb_opb                 | PushButtons_5B      | lit |

| General Purpose IO                   | SOPB            | 0x40600000            | 0x4060ffff      | 64K      |             | mb_opb                 | RS232_Uart_1        |     |

| Interrupt Control                    | SOPB            | 0x41400000            | 0x4140ffff      | 64K      |             | mb_opb                 | debug_module        |     |

| Memory Block                         | 2               |                       |                 |          |             |                        |                     |     |

| -Memory Controller                   |                 |                       |                 |          |             |                        |                     |     |

| PCI                                  |                 |                       |                 |          |             |                        |                     |     |

| Peripheral Controller                |                 |                       |                 |          |             |                        |                     |     |

| Processor                            |                 |                       |                 |          |             |                        |                     |     |

| Project Repository                   |                 |                       |                 |          |             |                        |                     |     |

| opb_customcore 1.00.a                |                 |                       |                 |          |             |                        |                     |     |

| -Reset Control                       |                 |                       |                 |          |             |                        |                     |     |

| Timer                                |                 |                       |                 |          |             |                        |                     |     |

| 🖶 Utility                            |                 |                       |                 |          |             |                        |                     |     |

| ··· Verification                     | -               |                       |                 |          |             |                        |                     |     |

|                                      |                 | ssembly View1         |                 |          |             |                        |                     |     |

| 1                                    |                 |                       |                 |          |             |                        |                     |     |

| 1                                    |                 |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

| •                                    | 1               |                       |                 |          |             |                        |                     |     |

|                                      |                 |                       |                 |          |             |                        |                     |     |

| Output Warninga Errora               |                 |                       |                 |          |             |                        |                     |     |

| Output Warnings Errors               |                 |                       |                 |          |             |                        |                     |     |

# XPS - Generate Address Range For New IP

| 🚬 🕄 //////////////////////////////////                                                                                                                                                                                                                                                                                                                                     | Xilinx Platform                                                                                                                               | Studio - /users/jagro                 | n/388labs/chip              | pscopeM   | B/sys | tem.xmp - [System Assembly    | View1]               |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|-----------|-------|-------------------------------|----------------------|-----|

| Eile Edit View Project Hardware Softwar                                                                                                                                                                                                                                                                                                                                    | e Device <u>C</u> onfigurat                                                                                                                   | ion <u>D</u> ebug Si <u>m</u> ulation | n <u>W</u> indow <u>H</u> e | lp        |       |                               |                      | يل_ |

| 🗗 🗶 🍋 🗠 🔂 👘 👘 💭 🔂 🐔 🔲                                                                                                                                                                                                                                                                                                                                                      | 🖻 🗛 🛛 🖻 🗗 😨                                                                                                                                   | • 🖸 💽 📃 🗞 🔝 🏀                         | 📗 🜌 Lipa 🛓                  | 🔊 🏠 🛛     | 태학 (  | 3 3 1 🔀 🕅 🔛 🕅                 | 6800000              |     |

|                                                                                                                                                                                                                                                                                                                                                                            | =≝Filters                                                                                                                                     |                                       |                             |           |       |                               |                      |     |

| Project Applications IP Catalog                                                                                                                                                                                                                                                                                                                                            | 🐣 🧲 Bus Inte                                                                                                                                  | rface 🤆 Ports 🖲 Add                   | iresses 🔤 Ge                | enerate A | ddres | ses                           |                      |     |

| •                                                                                                                                                                                                                                                                                                                                                                          | Name Add                                                                                                                                      | iress Base Address                    | High Addres                 | s Size    | 1.00  | Generate Addresses IP Type IP | Version Instance     |     |

| •                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                               | Base Address                          | High Address                | U U       |       | Generate Addresses IF Typi IF |                      |     |

| Name Version                                                                                                                                                                                                                                                                                                                                                               | SLMB                                                                                                                                          | 0-0000000                             | 0000000##                   | 16K       |       | ما مير الع                    | mb_opb<br>dimb_cntir |     |

| Communication High-Speed                                                                                                                                                                                                                                                                                                                                                   | SLMB                                                                                                                                          | 0x00000000<br>0x00000000              | 0x00003fff<br>0x00003fff    | 16K       |       | dlmb<br>ilmb                  | ilmb_cntlr           |     |

| Communication Low-Speed                                                                                                                                                                                                                                                                                                                                                    | SOPB                                                                                                                                          | 0x00000000                            | 0x4000fff                   | 64K       |       | mb opb                        | LEDs 4Bit            |     |

| DMA                                                                                                                                                                                                                                                                                                                                                                        | SOPB                                                                                                                                          | 0x40020000                            | 0x4000fff                   | 64K       |       | mb_opb                        | DIPSWs 4Bit          |     |

| B Debug                                                                                                                                                                                                                                                                                                                                                                    | SOPB                                                                                                                                          | 0x40020000                            | 0x4002fff                   | 64K       |       | mb_opb                        | PushButtons 5Bit     |     |

| PGA Reconfiguration                                                                                                                                                                                                                                                                                                                                                        | SOPB                                                                                                                                          | 0x40600000                            | 0x4004fff                   | 64K       |       | mb_opb                        | RS232_Uart_1         |     |

| General Purpose IO                                                                                                                                                                                                                                                                                                                                                         | SOPB                                                                                                                                          | 0x41400000                            | 0x4060fff                   | 64K       |       | mb opb                        | debug module         |     |

| Interrupt Control                                                                                                                                                                                                                                                                                                                                                          | SOPB                                                                                                                                          | 0x77000000                            | 0x7700fff                   | 64K       |       | mb_opb                        | opb customcore 0     |     |

| Memory Block                                                                                                                                                                                                                                                                                                                                                               | JOFB                                                                                                                                          | 0.77000000                            | 0.7700111                   | 041       | -     | 1110_000                      |                      |     |

| Hemory Controller                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                               |                                       |                             |           |       |                               |                      |     |

| B-PCI                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                               |                                       |                             |           |       |                               |                      |     |

| Peripheral Controller                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                               |                                       |                             |           |       |                               |                      |     |

| ⊕ Processor                                                                                                                                                                                                                                                                                                                                                                | 5                                                                                                                                             |                                       |                             |           |       |                               |                      |     |

| Project Repository                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                               |                                       |                             |           |       |                               |                      |     |

| opb customcore 1.00.a                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                               |                                       |                             |           |       |                               |                      |     |

| Beset Control                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                               |                                       |                             |           |       |                               |                      |     |

| ⊕-Timer                                                                                                                                                                                                                                                                                                                                                                    | 5                                                                                                                                             |                                       |                             |           |       |                               |                      |     |

| - Utility                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                               |                                       |                             |           |       |                               |                      |     |

| ⊞-Verification                                                                                                                                                                                                                                                                                                                                                             | -                                                                                                                                             |                                       |                             |           |       |                               |                      |     |

|                                                                                                                                                                                                                                                                                                                                                                            | System A                                                                                                                                      | ssembly View1                         |                             |           |       |                               |                      |     |

| ▲ (0x41400000-0x4140ffff) debug<br>INF0:MDT - Trying to assign som                                                                                                                                                                                                                                                                                                         | ne memory to Mic<br>bes not set Micr                                                                                                          | roBlaze reset ad                      |                             | s taken   |       |                               |                      |     |

| INFO:MDT - Address Generator dd<br>INFO:MDT - Standard address mag<br>Address Map for Processor micro<br>(bx0000000-0x00003fff) dlmb_<br>(0x40000000-0x4000ffff) Llmb_<br>(0x40020000-0x4002ffff) DIFSW<br>(0x40020000-0x4002ffff) DIFSW<br>(0x40040000-0x4006ffff) RS232<br>(0x41400000-0x4140ffff) gbu_<br>(0x7000000-0x7700fff) obb_<br>INFO:MDT - Address map generate | blaze_0<br>_cntlr dlmb<br>_cntlr ilmb<br>_4Bit mb_opt<br>%s_4Bit mb_opt<br>Buttons_5Bit<br>2_Uart_1 mb_opt<br>g_module mb_opt<br>customcore_0 | mb_opb                                |                             |           |       |                               |                      |     |

| INFO:MDT - Standard address mag<br>Address Map for Processor micro<br>(0x0000000-0x00003fff) dlmb_<br>(0x0000000-0x0003fff) iLEDs_<br>(0x40020000-0x4002ffff) LEDs_<br>(0x40020000-0x4002ffff) DISN<br>(0x40600000-0x4004ffff) Push<br>(0x40600000-0x4140ffff) debug<br>(0x7700000-0x7700ffff) opb_c                                                                       | blaze_0<br>_cntlr dlmb<br>_cntlr ilmb<br>_4Bit mb_opt<br>%s_4Bit mb_opt<br>Buttons_5Bit<br>2_Uart_1 mb_opt<br>g_module mb_opt<br>customcore_0 | mb_opb                                |                             |           |       |                               |                      |     |

### Now What?

- The custom IP core is now...

- Instantiated within the system

- Via "Add IP".

- Connected to the system.

- Via bus connection and address generation.

- Now, how do we use it?

- We must write an application that "talks" to it.

- How do you communicate with IP?

- You know it's address (hopefully).

- How does a CPU communicate with addresses???

### Memory-Mapped I/O

- CPUs can read/write to addresses.

- Usually addresses refer to memory locations.

- This is not always true.

- Anything can be "mapped" into an address space.

- It doesn't have to be memory.

- Reads: request information from a specific source.

- Writes: send information to a specific source.

- What programming constructs do we need?

### Pointers!!!

### • Pointers:

- A programming construct.

- Used to "point" to a specific location.

- Often times memory.

- Features:

- A location to point to (address).

- Something being pointed at (data).

### **Pointer Example**

- A pointer to an integer stored at location 0x5000000.

- *int* \**myPtr* = (*int*\*)0*x*5000000;

- Writing data to the location:

- \*myPtr = <newData>;

- Reading data from the location:

- dataAtLocation = \*myPtr;

- Changing the location being pointed at:

- myPtr = <newLocation>;

- What is the "\*" doing????

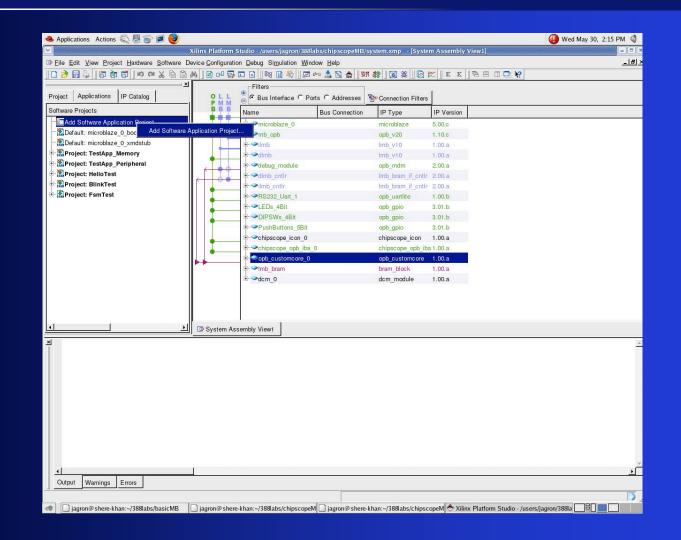

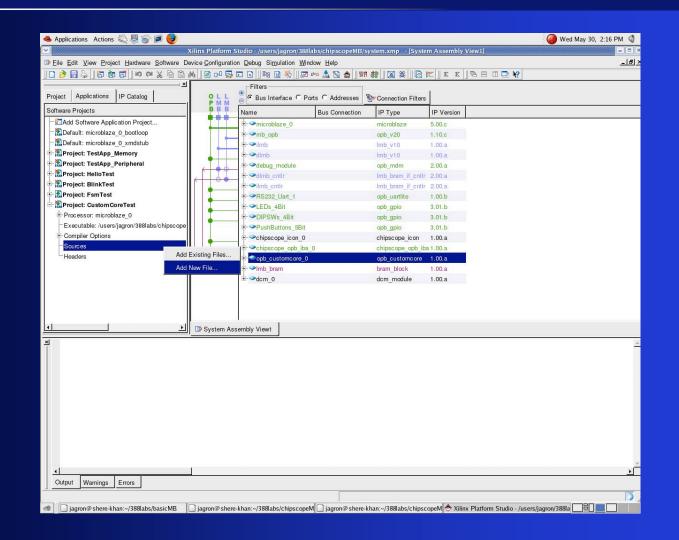

### **XPS - Creating An Application**